上期我們簡單描述了Eisc系統(tǒng),這期我們更加深入地討論下���,Eisc系統(tǒng)��,并比較一下它與其他主流系統(tǒng)的優(yōu)缺點(diǎn)����。

16bit 固定長度可擴(kuò)展結(jié)構(gòu)

ESIC結(jié)構(gòu)基本的指令代碼長度是16bit . 32bit 指令結(jié)構(gòu)系統(tǒng)也是為特定的領(lǐng)域給出擴(kuò)展的偏移量。使芯片具有較小的基本指令程序代碼和較低的成本�����。因此ESIC的16bit結(jié)構(gòu)對于成本敏感的產(chǎn)品十分適合�����。

16bit寄存器系統(tǒng)

16bit寄存器結(jié)構(gòu)對于帶寬和存儲器效率最理想�����。 EISC對通信提供16bit的通用寄存器�����。

擴(kuò)展寄存器和標(biāo)志

EISC 結(jié)構(gòu)的關(guān)鍵是通過設(shè)置擴(kuò)展寄存器和標(biāo)志(E)使系統(tǒng)可以進(jìn)行32bits擴(kuò)展應(yīng)用����。 當(dāng)一個操作數(shù)被寫入32bit擴(kuò)展寄存器(i.e.%ER)的時候E標(biāo)志就被設(shè)置了���。LERI 指令(Load Extension Register Immediate) 執(zhí)行有條件轉(zhuǎn)變(由E標(biāo)志控制)并且裝入合成的長立即操作數(shù)到擴(kuò)展的寄存器中���。

可升級的公共操作代碼

由于ESIC是以操作數(shù)可擴(kuò)展為目的而開發(fā)的結(jié)構(gòu),無論16/32/64bit,基本的操作代碼是公共的.僅僅根據(jù)寄存器尺寸的變化而對指令數(shù)量作小的調(diào)整��。 因此,EISC是達(dá)到完全可升級設(shè)計(jì)的第一個結(jié)構(gòu)�。

簡單的硬件結(jié)構(gòu)

和RISC相比,EISC是一個 16bit 固定的長度指令結(jié)構(gòu)因此有簡單指令程序。 例如adc公司最簡單的32bit結(jié)構(gòu)的SE3208有8個一般寄存器����,電路數(shù)量僅為20K門, 是所有 32bit微處理器中間的最少的。 因?yàn)?EISC 處理機(jī)具有很小的指令程序, 他們可以使用更小的存儲器, 這對于終端用戶來說就是成本的降低��。

高性能

通常來說��,當(dāng)指令程序變得更簡單時,CPU時鐘性能將會提高��。 因此, 在EISC結(jié)構(gòu)下處理器性能會更好����。 具有LERI指令結(jié)構(gòu)的微處理器和同等的RICS處理器相比指令數(shù)量顯著減小��,但指令的執(zhí)行時間幾乎和RISC相當(dāng)����;和同等級的CISC處理器相比指令數(shù)量相當(dāng)�,但指令的執(zhí)行時間比CISC快的多�����。

高代碼密度

對于SOC產(chǎn)品的嵌入的應(yīng)用十分強(qiáng)調(diào)微處理器、存儲器和輸入輸出等電路的綜合性能�。 程序ROM 在這種類型的上占有最大的空間。 因此減少程序大小就是降低成本��。

EISC的通過擴(kuò)展寄存器和擴(kuò)展標(biāo)志位來使固定的16bit指令長度增長的方式具有很高的代碼密度以減小程序尺寸����。

低功耗的結(jié)構(gòu)

高代碼密度結(jié)構(gòu)所需的程序尺寸一定是最小的����。同時由于邏輯門電路的減少使得結(jié)構(gòu)的功耗大大降低。 硬件由簡單的結(jié)構(gòu)構(gòu)成并且CMOS 邏輯門的狀態(tài)無須頻繁改變��,數(shù)據(jù)總線通信也大大減少�����。因此與其他微處理器比較, EISC由于它的簡單硬件和高的代碼密度是低功耗的結(jié)構(gòu)����。

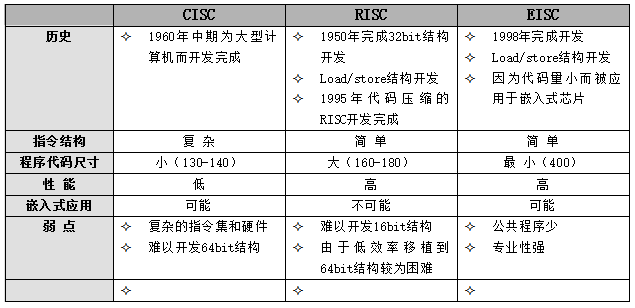

CISC/RISC/EISC 比較表